# NORME INTERNATIONALE INTERNATIONAL STANDARD

CEI IEC 748-20-1

QC 763000

Première édition First edition 1994-02

Dispositifs à semiconducteurs – Circuits intégrés –

# Partie 20:

Spécification générique pour les circuits intégrés à couches et les circuits intégrés hybrides à couches – N

Section 1: Exigences pour l'examen visuel interne

Semiconductor devices – Integrated circuits –

# **Part 20:**

Generic specification for film integrated circuits and hybrid film integrated circuits –

Section 1: Requirements for internal visual examination

#### Numéros des publications

Depuis le 1er janvier 1997, les publications de la CEI sont numérotées à partir de 60000.

#### Publications consolidées

Les versions consolidées de certaines publications de la CEI incorporant les amendements sont disponibles. Par exemple, les numéros d'édition 1.0, 1.1 et 1.2 indiquent respectivement la publication de base, la publication de base incorporant l'amendement 1, et la publication de base incorporant les amendements 1 et 2.

#### Validité de la présente publication

Le contenu technique des publications de la CEI est constamment revu par la CEI afin qu'il reflète l'état actuel de la technique.

Des renseignements relatifs à la date de reconfirmation de la publication sont disponibles dans le Catalogue de la CEI.

Les renseignements relatifs à des questions à l'étude et des travaux en cours entrepris par le comité technique qui a établi cette publication, ainsi que la liste des publications établies, se trouvent dans les documents cidessous:

- «Site web» de la CEI\*

- Catalogue des publications de la CEI

Publié annuellement et mis à jour régulièrement

(Catalogue en ligne)\*

- Bulletin de la CEI

Disponible à la fois au «site web» de la CEE

et comme périodique imprimé

# Terminologie, symboles graphiques et littéraux

En ce qui concerne la terminologie générale, le lecteur se reportera à la CEI 60050: Vocabulaire Electrotechnique International (VEI).

Pour les symboles graphiques, les symboles littéraux et les signes d'usage général approuvés par la CEI, le lecteur consultera la CEI 60027: Symboles littéraux à utiliser en électrotechnique, la CEI 60417: Symboles graphiques utilisables sur le matériel. Index, relevé et compilation des feuilles individuelles, et la CEI 60617: Symboles graphiques pour schémas.

\* Voir adresse «site web» sur la page de titre.

#### Numbering

As from 1 January 1997 all IEC publications are issued with a designation in the 60000 series.

#### **Consolidated publications**

Consolidated versions of some IEC publications including amendments are available. For example, edition numbers 1.0, 1.1 and 1.2 refer, respectively, to the base publication, the base publication incorporating amendment 1 and the base publication incorporating amendments 1 and 2.

# Validity of this publication

The technical content of IEC publications is kept under constant review by the IEC, thus ensuring that the content reflects current technology.

Information relating to the date of the reconfirmation of the publication is available in the IEC catalogue.

Information on the subjects under consideration and work in progress undertaken by the technical committee which has prepared this publication, as well as the list of publications issued, is to be found at the following IEC sources:

- IEC web site\*

- Catalogue of IEC publications

Published yearly with regular updates

(On-line catalogue)\*

- IEC Bulletin

Available both at the IEC web site\* and as a printed periodical

# Terminology, graphical and letter symbols

For general terminology, readers are referred to IEC 60050: *International Electrotechnical Vocabulary* (IEV).

For graphical symbols, and letter symbols and signs approved by the IEC for general use, readers are referred to publications IEC 60027: Letter symbols to be used in electrical technology, IEC 60417: Graphical symbols for use on equipment. Index, survey and compilation of the single sheets and IEC 60617: Graphical symbols for diagrams.

\* See web site address on title page.

# NORME INTERNATIONALE INTERNATIONAL STANDARD

CEI IEC 748-20-1

QC 763000

Première édition First edition 1994-02

Dispositifs à semiconducteurs – Circuits intégrés –

# Partie 20:

Spécification générique pour les circuits intégrés à couches et les circuits intégrés hybrides à couches –

Section 1: Exigences pour l'examen visuel interne

Semiconductor devices – Integrated circuits –

# Part 20:

Generic specification for film integrated circuits and hybrid film integrated circuits –

Section 1: Requirements for internal visual examination

© CEI 1994 Droits de reproduction réservés — Copyright – all rights reserved

Aucune partie de cette publication ne peut être reproduite ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et les microfilms, sans l'accord écrit de l'éditeur.

No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher.

Bureau Central de la Commission Electrotechnique Internationale 3, rue de Varembé Genève, Suisse

Commission Electrotechnique Internationale International Electrotechnical Commission Международная Электротехническая Комиссия CODE PRIX

PRICE CODE

Pour prix, voir catalogue en vigueur For price, see current catalogue

# SOMMAIRE

|       |      | Pa                                                                           | ages |

|-------|------|------------------------------------------------------------------------------|------|

| AV    | ANT- | PROPOS                                                                       | 4    |

| Artic | des  |                                                                              |      |

| 1     | Dom  | aine d'application et objet                                                  | 6    |

|       | 1.1  | But                                                                          | 6    |

|       | 1.2  | But                                                                          | 6    |

|       | 1.3  | Matérial d'avamen                                                            | 6    |

|       | 1.4  | Environnement de l'examen  Grossissement  Définitions                        | 6    |

|       | 1.5  | Grossissement                                                                | 6    |

|       | 1.6  | Définitions                                                                  | 6    |

|       | 1.7  | Interprétations                                                              | 10   |

|       | 1.8  | Interprétations                                                              | 10   |

|       |      | strat et processus  Substrat  Processus                                      |      |

| 2     | Sub  | strat et processus                                                           | 10   |

|       | 2.1  | Substrat                                                                     | 10   |

|       | 2.2  | Processus                                                                    | 12   |

|       |      |                                                                              |      |

| 3     | Asse | emblage – Fixation mécanique et connexion électrique des parties du substrat |      |

|       | 3.1  | Composants rapportés                                                         | 16   |

|       | 3.2  | Méthode d'assemblage                                                         | 16   |

|       |      | Mr.                                                                          |      |

| 4     | Ass  | emblage – Fixation mécanique et connexion électrique du substrat au boîtier  |      |

|       | 4.1  | Généralités                                                                  |      |

|       | 4.2  | Soudure et adhésif organique                                                 | 20   |

| _     | Into | rconnexions de fils                                                          | 22   |

| 5     | me   |                                                                              |      |

|       | 5.1  | Généralités                                                                  |      |

|       | 5.2  | Soudure par boule d'or et en lingot                                          |      |

|       | 5.3  |                                                                              |      |

|       | 5,4  | Soudure sans queue (en croissant)                                            |      |

| 1     | 5.5  | Soudure en lingot                                                            |      |

| ·     | 5.6  | Soudures superposées                                                         |      |

|       | 5.7  | Soudure des conducteurs poutres                                              |      |

|       | 5.8  | Critères pour les fils                                                       | 20   |

| 6     | Con  | ditions de boîtier                                                           | 26   |

| 7     | Mate | ériau étranger                                                               | 26   |

|       |      |                                                                              | 25   |

# CONTENTS

|      |                                                                                    | P                                                                                             | age |  |  |  |  |

|------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----|--|--|--|--|

| FO   | OREWORD5                                                                           |                                                                                               |     |  |  |  |  |

| Clau | ıse                                                                                |                                                                                               |     |  |  |  |  |

| 1    | Scop                                                                               | be and object                                                                                 | 7   |  |  |  |  |

|      | 1.1                                                                                | Purpose                                                                                       | 7   |  |  |  |  |

|      | 1.2                                                                                | Sequence of inspections                                                                       | 7   |  |  |  |  |

|      | 1.3                                                                                | Inspection apparatus                                                                          | 7   |  |  |  |  |

|      | 1.4                                                                                |                                                                                               | 7   |  |  |  |  |

|      | 1.5                                                                                | Magnification                                                                                 | 7   |  |  |  |  |

|      | 1.6                                                                                | Definitions                                                                                   | 7   |  |  |  |  |

|      | 1.7                                                                                | Interpretations                                                                               | 11  |  |  |  |  |

|      | 1.8                                                                                | Inspection environment  Magnification  Definitions  Interpretations  Alternative test methods | 11  |  |  |  |  |

| 2    | Sub                                                                                | Substrate  Processes                                                                          | 11  |  |  |  |  |

| _    | Jub.                                                                               | Control of the processes                                                                      |     |  |  |  |  |

|      | 2.1                                                                                | Substrate                                                                                     | 11  |  |  |  |  |

|      | 2.2                                                                                | Processes                                                                                     | 13  |  |  |  |  |

| 3    | Asse                                                                               | embly – Mechanical attachment and electrical connection of parts to the substrate             | 17  |  |  |  |  |

|      | 3.1                                                                                | Added components                                                                              | 17  |  |  |  |  |

|      | 3.2                                                                                | Assembly method                                                                               | 17  |  |  |  |  |

|      | J.Z                                                                                | Assembly method                                                                               |     |  |  |  |  |

| 4    | Assembly – Mechanical attachment and electrical connection of substrate to package |                                                                                               |     |  |  |  |  |

|      | 4.1                                                                                | General                                                                                       | 21  |  |  |  |  |

|      | 4.2                                                                                |                                                                                               |     |  |  |  |  |

|      |                                                                                    |                                                                                               |     |  |  |  |  |

| 5    | Wire                                                                               | interconnections                                                                              | 23  |  |  |  |  |

|      | 5.1                                                                                | General                                                                                       | 23  |  |  |  |  |

|      | 5.2                                                                                | Gold ball and wedge bonds                                                                     | 23  |  |  |  |  |

|      | 5.3                                                                                |                                                                                               |     |  |  |  |  |

|      | 5.4                                                                                | Tail-less (crescent) bonds                                                                    | 23  |  |  |  |  |

|      |                                                                                    | Wedge bonds                                                                                   | 25  |  |  |  |  |

|      | 5.6                                                                                | Compound bonds                                                                                | 25  |  |  |  |  |

|      | 5.7                                                                                | Beam lead bonds                                                                               | 25  |  |  |  |  |

|      | 5.8                                                                                | Criteria for wires                                                                            | 27  |  |  |  |  |

| 6    | Dool                                                                               | kage conditions                                                                               | 27  |  |  |  |  |

| 6    | raci                                                                               | Adde Colliditions                                                                             |     |  |  |  |  |

| 7    | Fore                                                                               | ign material                                                                                  | 27  |  |  |  |  |

| Fic  | urae                                                                               |                                                                                               | 29  |  |  |  |  |

# COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE

# DISPOSITIFS À SEMICONDUCTEURS – Circuits intégrés –

Partie 20: Spécification générique pour les circuits intégrés à couches et les circuits intégrés hybrides à couches –

# Section 1: Exigences pour l'examen visuel interne

#### **AVANT-PROPOS**

- 1) La CEI (Commission Electrotechnique Internationale) est une organisation mondiale de normalisation composée de l'ensemble des comités électrotechniques nationaux (Comités nationaux de la CEI). La CEI a pour objet de favoriser la coopération internationale pour toutes les questions de normalisation dans les domaines de l'électricité et de l'électronique. A cet effet, la CEI, entre autres activités, publie des Normes internationales. Leur élaboration est confiée à des comités d'études, aux travaux desquels tout Comité national intéressé par le sujet traité peut participer. Les organisations internationales, gouvernementales et non gouvernementales, en liaison avec la CEI, participent également aux travaux. La CEI collabore étroitement avec l'Organisation Internationale de Normalisation (ISO), selon des conditions fixées par accord entre les deux organisations.

- 2) Les décisions ou accords officiels de la CEI en ce qui concerne les questions techniques, préparés par les comités d'études où sont représentés tous les Comités nationaux s'intéressant à ces questions, expriment dans la plus grande mesure possible un accord international sur les sujets examinés.

- 3) Ces décisions constituent des recommandations internationales publiées sous forme de normes, de rapports techniques ou de guides et agréées comme telles par les Comités nationaux.

- 4) Dans le but d'encourager l'unification internationale, les Comités nationaux de la CEI s'engagent à appliquer de façon transparente, dans toute la mesure possible, les Normes internationales de la CEI dans leurs normes nationales et régionales. Toute divergence entre la norme de la CEI et la norme nationale ou régionale correspondante doit être indiquée en termes clairs dans cette dernière.

La Norme internationale CEI 748-20-1 a été établie par le sous-comité 47A: Circuits intégrés, du comité d'études 47 de la CEI: Dispositifs à semiconducteurs.

Cette norme concerne l'examen visuel interne des circuits intégrés à couche et des circuits intégrés hybrides à couches

Le texte de cette norme est issu des documents suivants:

| DIS             | Rapport de vote |

|-----------------|-----------------|

| 47A(BC)272/272A | 47A(BC)285      |

Le rapport de vote indiqué dans le tableau ci-dessus donne toute information sur le vote ayant abouti à l'approbation de cette norme.

Le numéro QC qui figure sur la page de couverture de la présente publication est le numéro de la spécification dans le système CEI d'assurance de la qualité des composants électroniques (IECQ).

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

# SEMICONDUCTOR DEVICES – Integrated circuits –

Part 20: Generic specification for film integrated circuits and hybrid film integrated circuits –

Section 1: Requirements for internal visual examination

#### **FOREWORD**

- 1) The IEC (International Electrotechnical Commission) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of the IEC is to promote international cooperation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, the IEC publishes International Standards. Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. The IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of the IEC on technical matters, prepared by technical committees on which all the National Committees having a special interest therein are represented, express, as nearly as possible, an international consensus of opinion on the subjects dealt with.

- 3) They have the form of recommendations for international use published in the form of standards, technical reports or guides and they are accepted by the National Committees in that sense.

- 4) In order to promote international unification, IEO National Committees undertake to apply IEC International Standards transparently to the maximum extent possible in their national and regional standards. Any divergence between the IEC Standard and the corresponding national or regional standard shall be clearly indicated in the latter.

International Standard IEC 748-20-1 has been prepared by sub-committee 47A: Integrated circuits, of IEC technical committee 47: Semiconductor devices.

This standard concerns internal visual examination for film and hybrid film integrated circuits.

The text of this standard is based on the following documents:

| DIS             | Report on voting |

|-----------------|------------------|

| 47A(CO)272/272A | 47A(CO)285       |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

The QC number that appears on the front cover of this publication is the specification number in the IEC Quality Assessment System for Electronic Components (IECQ).

# DISPOSITIFS À SEMICONDUCTEURS – Circuits intégrés –

# Partie 20: Spécification générique pour les circuits intégrés à couches et les circuits intégrés hybrides à couches –

# Section 1: Exigences pour l'examen visuel interne

#### 1 Domaine d'application et objet

#### 1.1 But

Le but de ces examens est de vérifier les matériaux internes, la construction et la qualité d'exécution des circuits intégrés à couches et hybrides à couches (C et CIHC).

Ces examens seront normalement effectués préalablement à la fermeture du boîtier ou à l'encapsulation afin de détecter et d'éliminer les C et CIHC dont les défauts internes pourraient mener à un échec du dispositif dans son fonctionnement normal. D'autres critères d'acceptation peuvent être négociés avec l'acheteur ou le fournisseur.

#### 1.2 Séquence d'examens

L'ordre dans lequel se présentent les examens n'est pas obligatoire et peut être modifié par le fabricant selon sa convenance. Tout aspect susceptible d'être caché suite à un processus d'assemblage doit être examiné avant ce processus.

#### 1.3 Matériel d'examen

Le matériel d'essai doit comporter des appareils optiques capables du ou des grossissements spécifiés et toutes normes visuelles (calibres, dessins, photos, etc.) nécessaires pour réaliser un examen efficacement et qui permettent à l'opérateur de prendre des décisions objectives concernant l'acceptabilité de l'appareil examiné. Un système de fixation adéquat doit être fourni pour manipuler les appareils durant l'examen, permettant un fonctionnement correct sans occasionner de dommage aux éléments testés.

### 1.4 Environnement de l'examen

A l'étude.

#### 1.5 *Grossissement*

Un examen à «fort grossissement» (100 x à 200 x) est normalement réalisé à l'aide d'un microscope perpendiculaire à la surface sur laquelle se trouve l'appareil normalement éclairé.

Un examen à «faible grossissement» (10 x à 100 x) est normalement réalisé à l'aide d'un microscope monoculaire, binoculaire ou d'un microscope stéréoscopique à un angle et avec un éclairage approprié.

#### 1.6 Définitions

Pour les besoins de la présente section de la CEI 748-20, les définitions suivantes s'appliquent.

#### 1.6.1 Zone de circuit actif

Tous éléments de circuit fonctionnels, toutes métallisations fonctionnelles ou toutes leurs combinaisons.

# SEMICONDUCTOR DEVICES – Integrated circuits –

# Part 20: Generic specification for film integrated circuits and hybrid film integrated circuits –

# Section 1: Requirements for internal visual examination

# 1 Scope and object

### 1.1 Purpose

The purpose of these examinations is to check the internal materials, construction and workmanship of film and hybrid integrated circuits (F and HFICs).

These examinations will normally be used prior to tapping or encapsulation to detect and eliminate the F and HFICs with internal defects that could lead to device failure in normal application. Other acceptance criteria may be agreed upon with the purchaser or supplier.

### 1.2 Sequence of inspections

The order in which inspections are presented is not a required order of examination and may be varied at the discretion of the manufacturer. Any aspect which may be obscured by a subsequent assembly process shall be examined before that process.

#### 1.3 Inspection apparatus

The apparatus for this test shall include optical equipment capable of the specified magnification(s) and any visual standard (gauges, drawings, photographs, etc.) necessary to perform an effective examination and enable the operator to make objective decisions as to the acceptability of the device being examined. Adequate fixtures shall be provided for handling devices during examination to promote efficient operation without inflicting damage to the units.

#### 1.4 Inspection environment

Under consideration

#### 1.5 Magnification

"High magnification" (100 x to 200 x) inspection is normally performed with a microscope perpendicular to the relevant surface with the device under illumination.

"Low magnification" (10 x to 100 x) inspection is normally performed with a monocular, a binocular or a stereomicroscope at an appropriate angle and illumination.

#### 1.6 Definitions

For the purposes of this section of IEC 748-20, the following definitions apply.

#### 1.6.1 Active circuit area

All areas of functional circuit elements, operating metallization or any connected combinations thereof.

#### 1.6.2 Métallisation multicouche (pour les conducteurs)

Deux couches de métal ou plus ou tout autre matériau utilisé pour les interconnexions qui ne sont pas isolées les unes des autres.

#### 1.6.3 Métallisation de bord

Métallisation qui relie électriquement différentes couches de métallisation sur un substrat ou au niveau de sa tranche.

#### 1.6.4 Matériau étranger

Tout matériau non utilisé dans la fabrication du microcircuit ou toute partie du composant déplacée de sa position originale ou prévue, à l'intérieur du boîtier du microcircuit. Un matériau étranger qui, à l'examen visuel, apparaît comme opaque dans les conditions habituelles d'éclairage et de grossissement est considéré comme étant conducteur.

#### 1.6.5 Couche protectrice (passivation)

Couche de matériau isolant qui protège tout ou partie de la surface du substrat, comprenant la métallisation mais excluant les plots de raccordement, par exemple la vitrification, les décapants, etc.

#### 1.6.6 Couche isolante

Couche servant à isoler des niveaux conducteurs ou résistifs séparés.

#### 1.6.7 Sillon

Fente ou entaille faite par un procédé retirant le métal (par exemple un ajustage par laser ou par abrasion).

# 1.6.8 Métallisation multiniveau (conducteurs)

Deux niveaux de métal ou plus ou tout autre matériau utilisé pour des interconnexions isolées l'une de l'autre par la croissance ou le dépôt d'un matériau isolant et interconnecté par exemple par métallisation rapportée ou de contact.

#### 1.6.9 Plage de raccordement

Surface de métallisation exposée qui n'est pas couverte par la passivation.

#### 1.6.10 Connexions superposées

Soudure d'une connexion sur une autre.

#### 1.6.11 Trou métallisé

Métallisation qui connecte électriquement différents niveaux de métallisation sur ou dans un substrat via un ou plusieurs trous.

#### 1.6.12 Eraflure

Toute déchirure de la surface d'une couche.

### 1.6.2 Multi-layer metallization (for conductors)

Two or more layers of metal or any other material used for interconnections that are not isolated from each other.

### 1.6.3 Edge metallization

Metallization that electrically connects different layers of metallization on or within a substrate at its edge.

#### 1.6.4 Foreign material

Any material not used in the manufacture of the microcircuit or any in-built material that is displaced from its original or intended position within the microcircuit package Foreign material that appears opaque under those conditions of lighting and magnification used in routine visual inspection is considered as conductive.

#### 1.6.5 Protective layer (passivation)

Layer of insulating material that protects part or all of the substrate area, including metallization, but excluding connecting pads, for example glassivation, solder resist, etc.

#### 1.6.6 Isolating layer

Layer used to isolate separate conductive or resistive levels.

#### 1.6.7 Kerf

Slit or cut made by a material-removing process (for example laser or abrasive trimming).

# 1.6.8 Multilevel metallization (for conductors)

Two or more levels of metal or any other material used for interconnections that are isolated from each other by a grown or deposited insulating material and interconnected for example by vias or edge metallization.

#### 1.6.9 Bond pad area

That area of exposed metallization which is not covered by passivation.

# 1.6.10 / mpound bond

Bonding of one bond on top of another bond.

#### 1.6.11 Through-hole metallization

Metallization that electrically connects different levels of metallization on or within a substrate via a hole or holes.

### 1.6.12 Scratch

Any tearing defect on the surface of a layer.

#### 1.6.13 Eraflure légère

Rayure superficielle pouvant s'étendre sur la totalité d'une couche sans exposer ou endommager les couches sous-jacentes, ou déplacer latéralement la métallisation au-delà du bord du conducteur, par exemple par déformation mécanique.

#### 1.6.14 Mangue

Tout défaut dans une couche non provoqué par une rayure laissant apparaître un matériau sous-jacent.

#### 1.7 Interprétations

Le critère «s'il présente» est considéré comme satisfait lorsque l'image pull'apparence visuelle du dispositif examiné indique qu'une condition spécifique est visible.

Ceci ne demande pas à être confirmé par une autre méthode d'essai quelle qu'elle soit.

#### 1.8 Méthodes d'essai de substitution

Les exigences en matière d'examen visuel données ci-dessous ne sont pas nécessairement les seules méthodes pouvant être utilisées.

Cependant il convient que le fabricant assure l'Organisme National Habilité (ONH) que toute autre méthode apportera une assurance équivalente; sinon la méthode spécifiée sera utilisée.

# 2 Substrat et processus – Faible grossissement

#### 2.1 Substrat

Aucun dispositif ne doit être accepté s'il présente les défauts suivants:

- trous dans le substrat, sauf dans les trous de connexion, les orifices de montage des composants, utilisés ou non utilisés, ou les trous d'alignement;

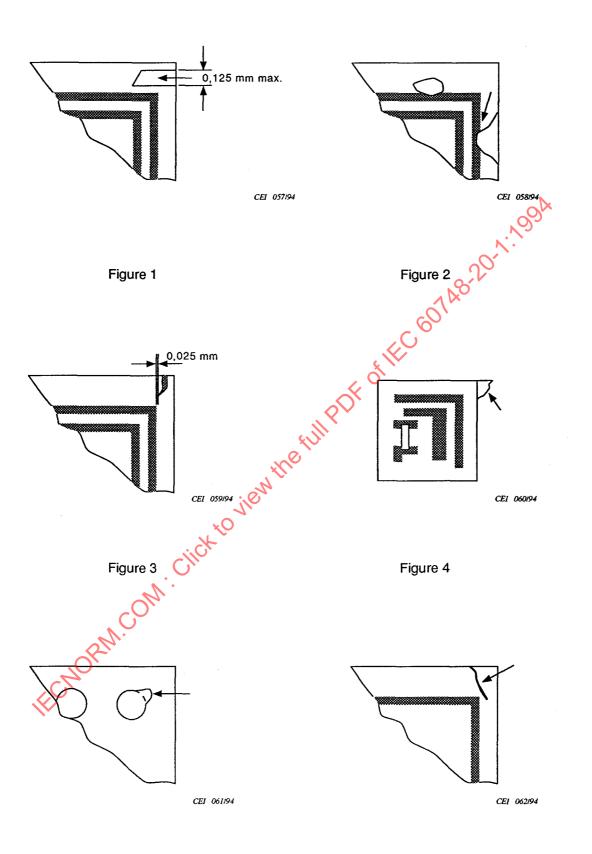

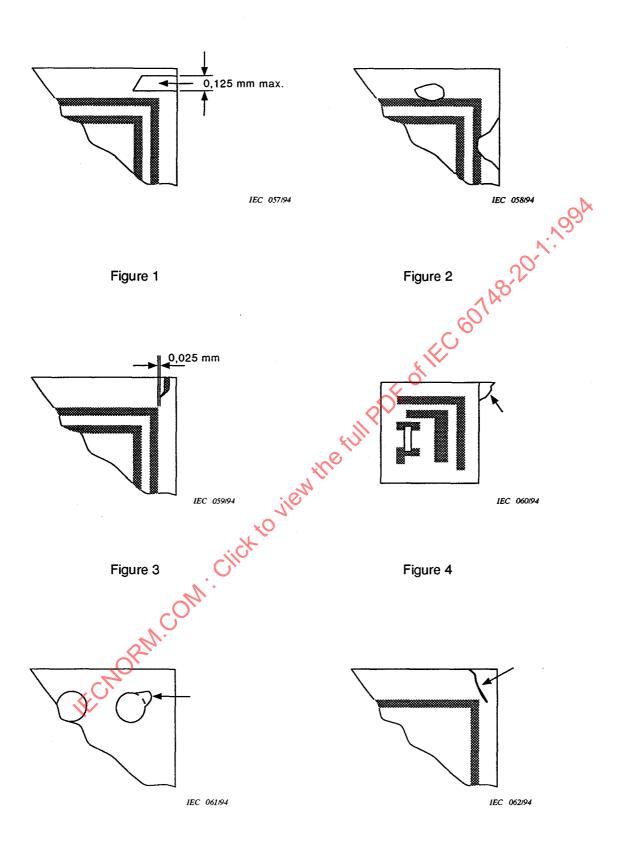

- toute fêlure excédant 0,125 mm de long et proche d'une partie fonctionnelle du circuit (voir figure 1);

- touf éclat réduisant la surface active (métallisée) d'un circuit (voir figure 2);

- toute fêlure se rapprochant d'une partie fonctionnelle d'un circuit à plus de 0,025 mm (voir figure 3);

- tout substrat comportant un morceau d'un autre substrat qui excède les dimensions permises par le dessin de l'ensemble (voir figure 4);

- tout substrat présentant une cassure autour d'un orifice de montage qui soit supérieure de 25 % à la circonférence de l'orifice prévu pour la fixation du substrat (voir figure 5);

- toute fêlure dont l'origine est sur un bord (voir figure 6).

#### 1.6.13 Cosmetic scratch

Shallow scratch which may extend completely across a layer and which does not expose or damage underlying layers, or laterally displace metallization beyond the edge of the conductor for example by mechanical deformation.

#### 1.6.14 Void

Any defect in a layer not caused by a scratch where underlying material is visible.

#### 1.7 Interpretations

Reference herein to "that exhibits" is considered satisfied when the visual image or visual appearance of the device under examination indicates a specific condition is present.

This does not require confirmation by any other method of testing.

#### 1.8 Alternative test methods

Visual examination requirements given below are not necessarily the only methods which can be used.

However, the manufacturer should satisfy the National Authorized Institution (NAI) that any alternative method will give equivalent assurance, otherwise the specified method is to be used.

#### 2 Substrate and processes – Low magnification

#### 2.1 Substrate

No device shall be acceptable that shows the following:

- holes through the substrate, except through lead holes, used or unused component mounting holes, or alignment holes;

- any crack that exceeds 0,125 mm in length and point toward an operating portion of the circuit (see figure 1);

- any chip out that reduces any active (metallized) circuit area (see figure 2);

- any crack that comes closer than 0,025 mm to an operating portion of the circuit (see figure 3);

- any substrate having attached portions of another substrate that exceed the substrate dimensions allowed by the assembly drawing (see figure 4);

- any substrate having a section broken out around any substrate mounting hole greater than 25 % of the mounting hole circumference when designed for substrate to post attachment (see figure 5);

- any crack that originates at an edge (see figure 6).

#### 2.2 Processus

#### 2.2.1 Conducteurs

Aucun dispositif ne doit être accepté s'il présente les défauts suivants:

- 1) éraflures de métallisation. (Une rayure est tout effet de déchirure, y compris des marques des points d'essai, à la surface de la métallisation);

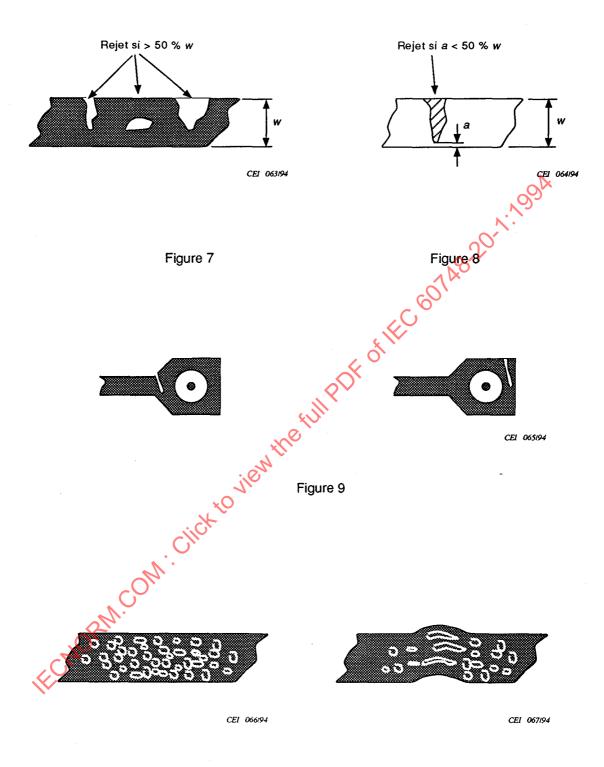

- éraflure de la métallisation, à l'exception des emplacements de soudure, qui expose le substrat ou le diélectrique sous-jacent, n'importe où sur sa longueur, et laisse intacte moins de 50 % de la largeur originale du métal (voir figure 7);

- éraflure de la métallisation multicouche qui expose le métal sous-jacent n'importe où sur sa longueur et laisse moins de 50 % de la largeur inchangée de la couche supérieure de métal (voir figure 8);

- éraflure dans l'emplacement de soudure ou la surface d'un congé de soudure qui expose le diélectrique ou le substrat sous-jacent et réduit la largeur de la bande métallisée assurant la liaison avec la zone de soudure à moins de 50 % de la largeur de la plus étroite bande d'interconnexion arrivant sur un emplacement de soudure. Si deux bandes ou plus arrivent sur le même emplacement de soudure, chacune d'elles doit être considérée séparément (voir figure 9);

#### 2) manques de métallisation

- manque(s) dans la métallisation, sauf pour les emplacements de soudure des fils ou des composants à poutre, qui laisse moins de 50 % de la largeur de métal inchangée (voir figure 7);

- manque(s) dans les emplacements de soudure des fils ou des composants à poutre qui laisse intacte une surface inférieure à deux fois celle de l'emplacement de soudure;

- m\u00e4nque(s) dans les emplacements de soudure des fils ou des composants \u00e4 poutre, y compris la surface du cong\u00e9 de soudure qui r\u00e9duit la largeur de la bande m\u00e9tallis\u00e9e assurant la liaison avec la zone de soudure \u00e0 moins de 50 % de la largeur de la plus \u00e9troite bande d'interconnexion arrivant sur un emplacement de soudure (voir figure 9).

NOTE - Si deux bandes ou plus arrivent sur un emplacement de soudure, il convient de considérer chacune d'elles séparément.

#### 3) corrosion de métallisation

toute corrosion de métallisation (voir figure 10);

#### 4) adhérence de métallisation

- tout soulèvement, écaillage ou boursouflure de la métallisation (voir figure 11);

- 5) marquage par les pointes d'essais de métallisation (les critères contenus en 1) et 2) doivent être appliqués en tant que limite aux dommages causés par les pointes d'essais);

#### 6) pontage de métallisation

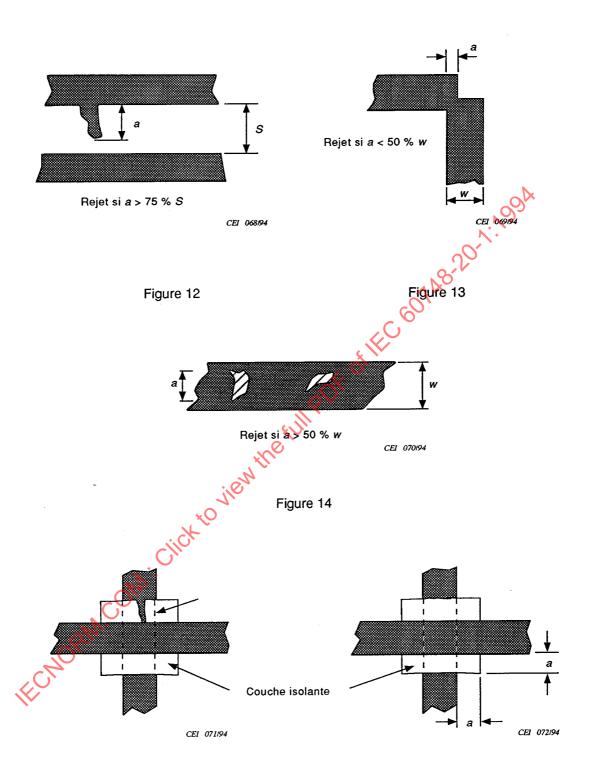

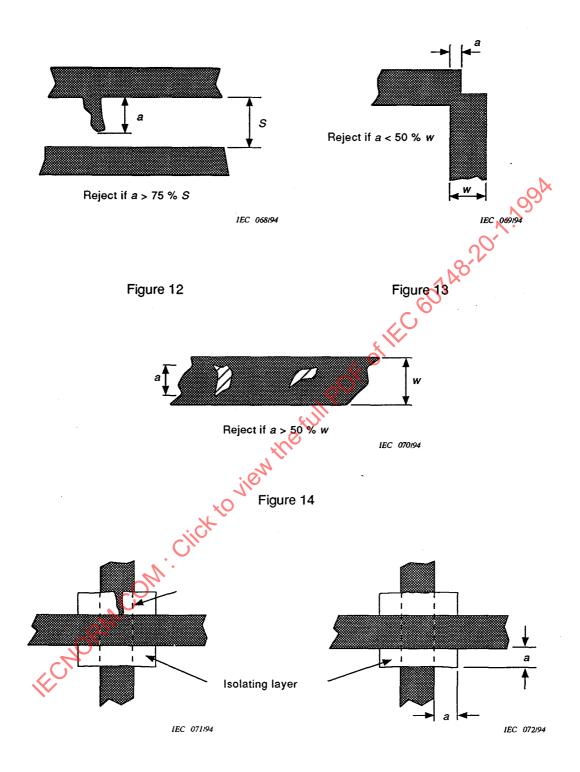

excroissance ou expansion du conducteur qui réduit la séparation existante entre deux éléments à moins de 25 % ou moins de 50 % de la distance minimale d'isolement prévue par conception, quelle que soit la plus grande (voir figure 12);

#### 2.2 Processes

#### 2.2.1 Conductors

No device shall be acceptable that shows the following:

- 1) metallization scratches (a scratch is any tearing effect, including probe marks, in the surface of the metallization);

- scratch in the metallization excluding bonding pads that exposes the substrate or underlying dielectric anywhere along its length and leaves less than 50 % of the metal width undisturbed (see figure 7);

- scratch in multilayered metallization that exposes the underlying metal anywhere along its length and leaves less than 50 % of the top layer metal width undisturbed (see figure 8);

- scratch in the bonding pad or fillet area that exposes the underlying dielectric or substrate and reduces the metallization path width connecting the bond to the interconnecting metallization to less than 50 % of the narrowest entering interconnect metallization stripe width. If two or more strips enter a bonding pad, each shall be considered separately (see figure 9);

#### 2) metallization voids

- void(s) in metallization except for wire or beam lead bonding pads that leaves less than 50 % of the metal width undisturbed (see figure 7);

- void(s) in the wire or beam lead bonding pad area that leaves an area less than twice the maximum allowable bond size undisturbed:

- void(s) in the wire or beam lead bonding pad, including fillet area that reduces the metallization path width connecting the bond to the interconnecting metallization to less than 50 % of the narrowest entering interconnect metallization strip width (see figure 9).

NOTE - If two or more strips enter a bonding pad, each should be considered separately.

- 3) metallization corrosion

- any metallization corrosion (see figure 10);

- 4) metallization adherence

- any metallization lifting, peeling or blistering (see figure 11);

- 5) metallization probing (criteria contained in 1) and 2) shall apply as limitations on probing damage);

- 6) metallization bridging

- protrusion or expansion of the conductor that reduces the existing separation from another element to less than 25 % or to less than 50 % of the minimum insulation distance specified in the design rules, whichever is the greater (see figure 12);

### 7) alignement de métallisation

désalignement dans lequel le débordement du conducteur est inférieur à 50 % de la largeur du conducteur le plus étroit (voir figure 13);

### 8) matériau étranger

- particule de matériau étranger dont l'une des dimensions est supérieure à 50 % de la largeur du conducteur (voir figure 14).

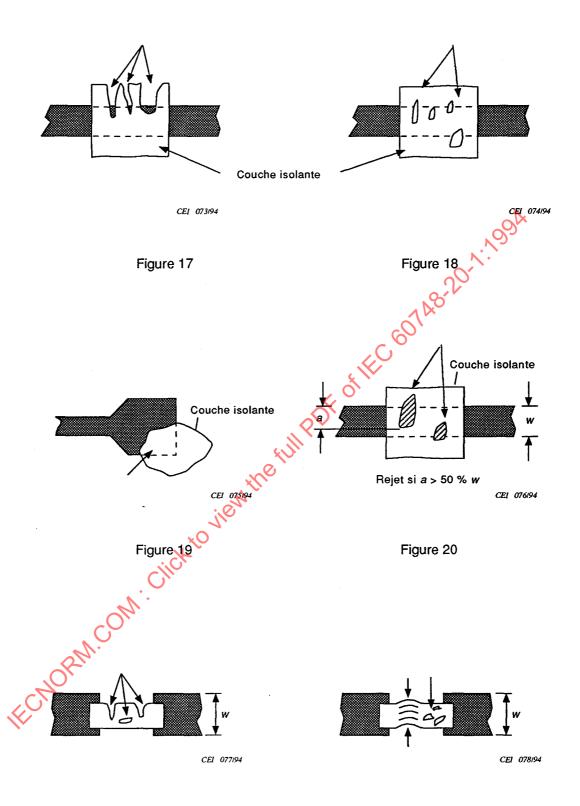

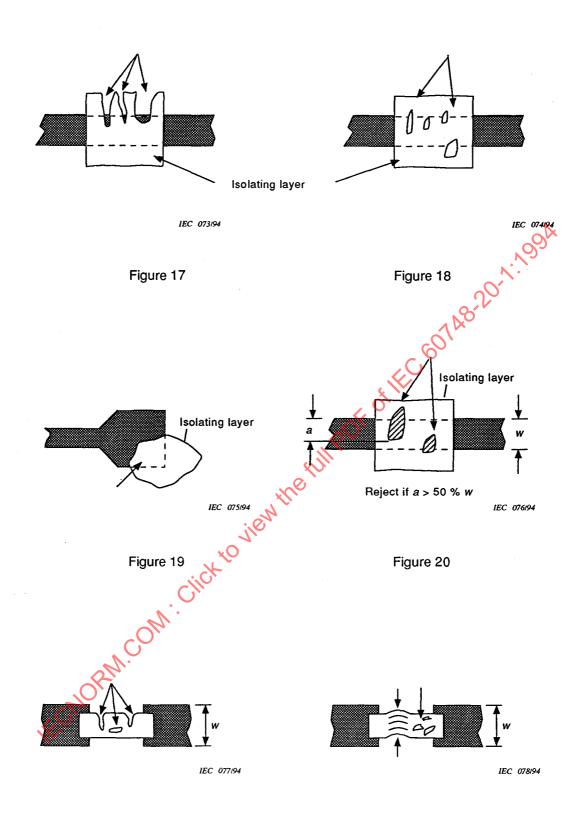

#### 2.2.2 Couche isolante

Aucun dispositif ne doit être accepté s'il présente les défauts suivants:

- éraflure ou manque sur une marche de diélectrique (voir figure 15);

- tout désalignement dans les transitions où le diélectrique n'est pas visible sur chaque côté à plus de 50 % de la distance minimale d'isolement prévue par conception entre les éléments du circuit (voir figure 16);

- éraflure, entaille ou manque qui expose le conducteur protégé (voir figure 17);

- boursouflure ou craquelure (voir figure 18);

- tout matériel diélectrique couvrant plus de 25 % d'une zone de raccordement ou de soudure (voir figure 19);

- particules permanentes ou matériau étranger dont l'une des dimensions est supérieure à 50 % de l'élément protégé (voir figure 20).

#### 2.2.3 Résistances

### 2.2.3.1 Résistances non ajustées

Aucun dispositif ne doit être accepté s'il présente les défauts suivants:

- éraflure, entaille ou manque dont l'une des dimensions est supérieure à 50 % de la largeur (voir figure 21).

- soulèvement, écaillage ou boursouflure (voir figure 22);

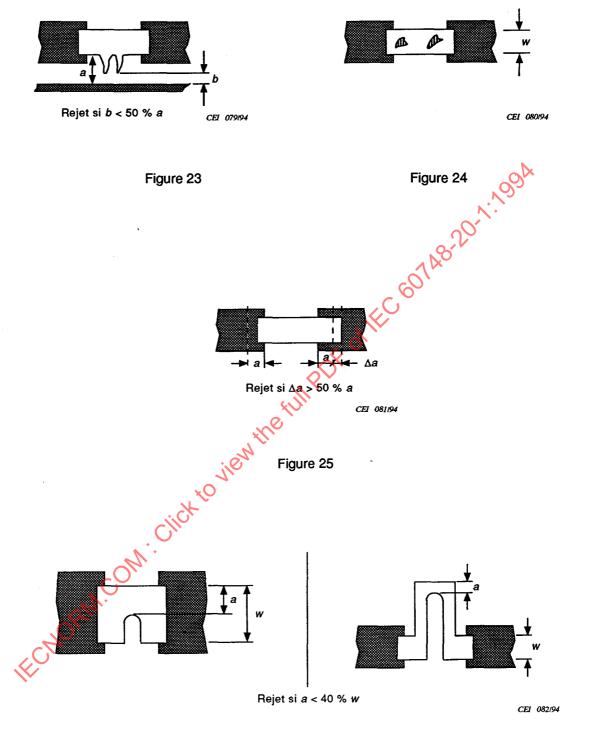

- excroissance ou expansion de la résistance qui réduit la séparation entre deux éléments à moins de 25 % ou moins de 50 % de la distance minimale d'isolement prévue par conception, quelle que soit la plus grande (voir figure 23);

- particule de matériau étranger dont l'une des dimensions est supérieure à 50 % de la largeur de la résistance (voir figure 24). L'ajustage ne doit pas toucher les particules étrangères;

- désalignement dans le sens de la longueur du débordement d'une résistance/d'un conducteur qui est supérieur à 50 % (voir figure 25);

- désalignement dans le sens de la largeur à l'extérieur des bornes du schéma du conducteur;

- toute modification notable dans les couleurs du matériau de résistance au niveau de la sortie résistance/conducteur.

#### 7) metallization alignment

- misalignment where the conductor overlap is less than 50 % of the width of the narrower conductor (see figure 13);

### 8) foreign material

- particle of foreign material with any dimension greater than 50 % of the conductor width (see figure 14).

# 2.2.2 Isolating layer

No device shall be acceptable that shows the following:

- scratch or void at or over a dielectric step (see figure 15);

- any misalignment in cross-overs where the dielectric is not visible on each side more than 50 % of the minimum designed insulation distance between circuit elements (see figure 16);

- a scratch, a nick or a void that exposes the buried conductor (see figure 17);

- blistering or crazing (see figure 18);

- any dielectric material covering more than 25 % of a bonding or soldering area (see figure 19);

- permanent particle or foreign material with any dimension greater than 50 % of the buried element width (see figure 20).

#### 2.2.3 Resistors

#### 2.2.3.1 Untrimmed resistors

No device shall be acceptable that shows the following:

- a scratch, a nick or a void with any dimension greater than 50 % of the width (see figure 21);

- lifting, peeling or blistering (see figure 22);

- protrusion or expansion of the resistor that reduces the existing separation from another element to less than 25 % or to less than 50 % of the minimum insulation distance specified in the design rules, whichever is the greater (see figure 23);

- particle of foreign material with any dimension greater than 50 % of the resistor width (see figure 24). Trimming shall not touch foreign particles;

- misalignment in the length direction of a resistor/conductor overlap greater than 50 % (see figure 25);

- misalignment in the width direction outside the boundaries of the conductor pattern;

- any sharp change in colour of the resistor material within the resistor/conductor termination.

#### 2.2.3.2 Résistances ajustées

Aucun dispositif ne doit être accepté s'il présente les défaillances décrites en 2.2.3.1 ou les suivantes:

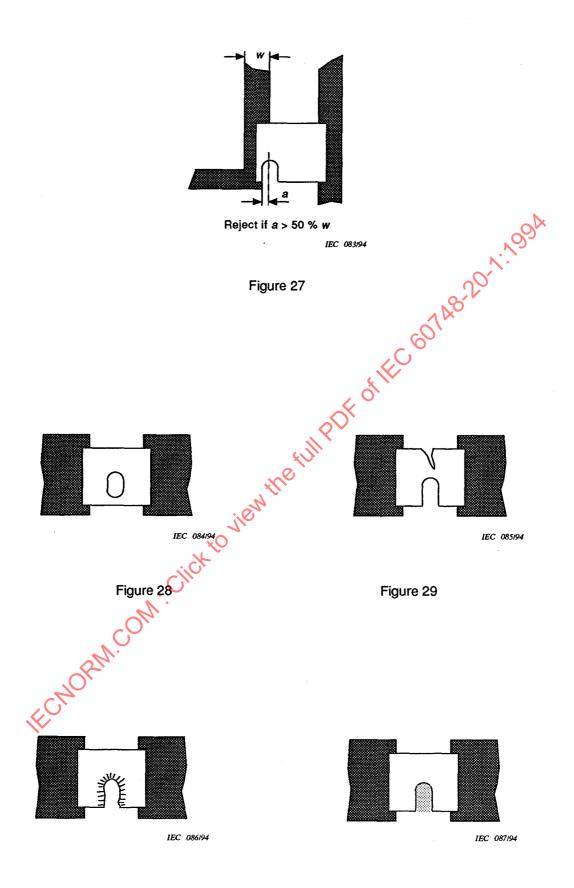

#### 1) résistances ajustées par abrasion

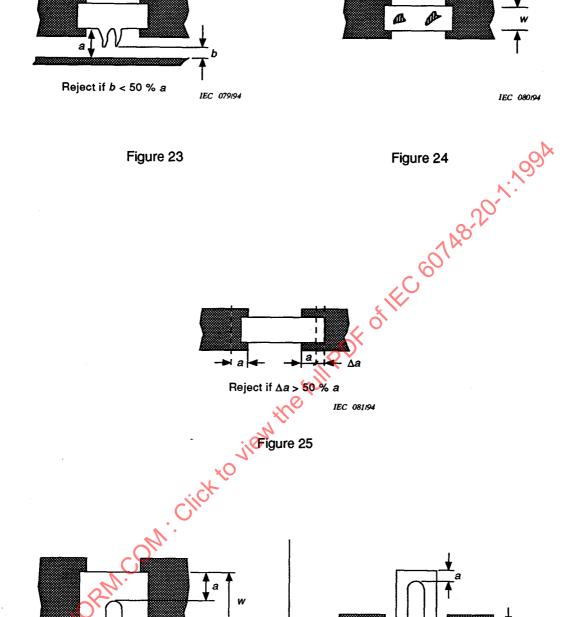

- la largeur minimale d'une résistance restant après ajustage doit être de 40 % (voir figure 26) sauf quand il apparaît que la densité maximale usuelle autorisée par les règles de conception n'est pas dépassée;

- largeur de la sortie réduite de plus de 50 % (voir figure 27);

- pontage pour la découpe d'ajustage (voir figure 28);

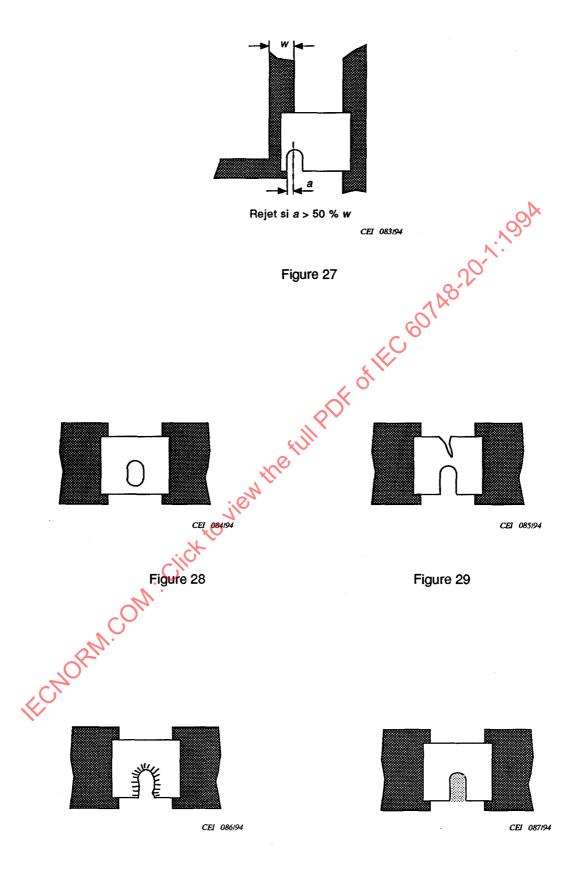

- éraflure, entaille ou manque à l'opposé d'un sillon d'ajustage qui diminue la largeur des résistances à 40 % (voir figure 29);

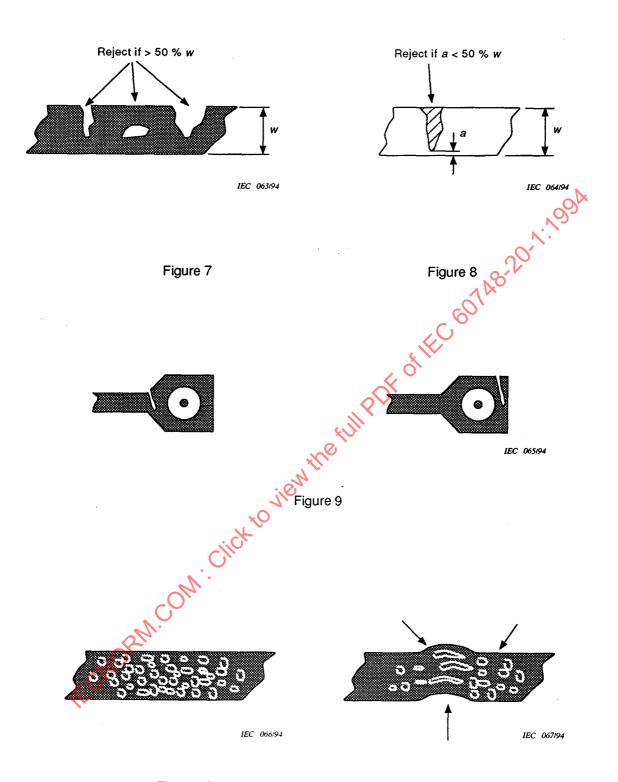

- microfissure et bordures grossières du matériau de la résistance (voir figure 30);

- résidu du matériau de la résistance dans la découpe d'ajustage (voir figure 31);

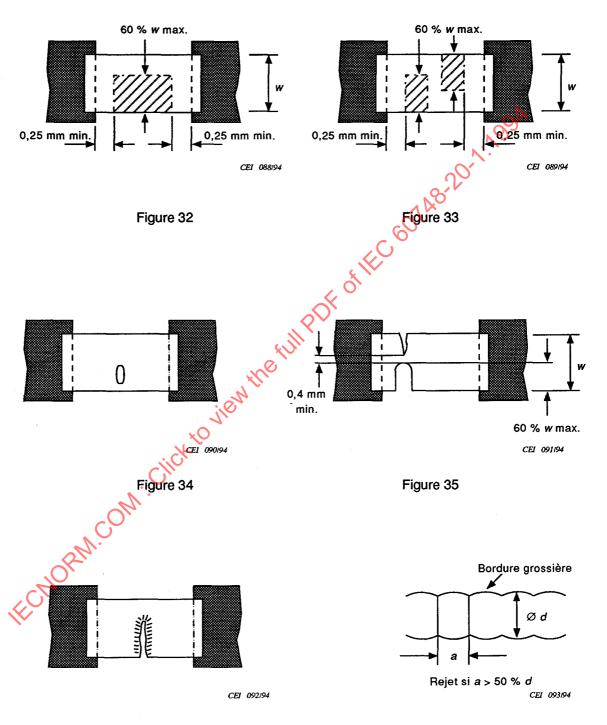

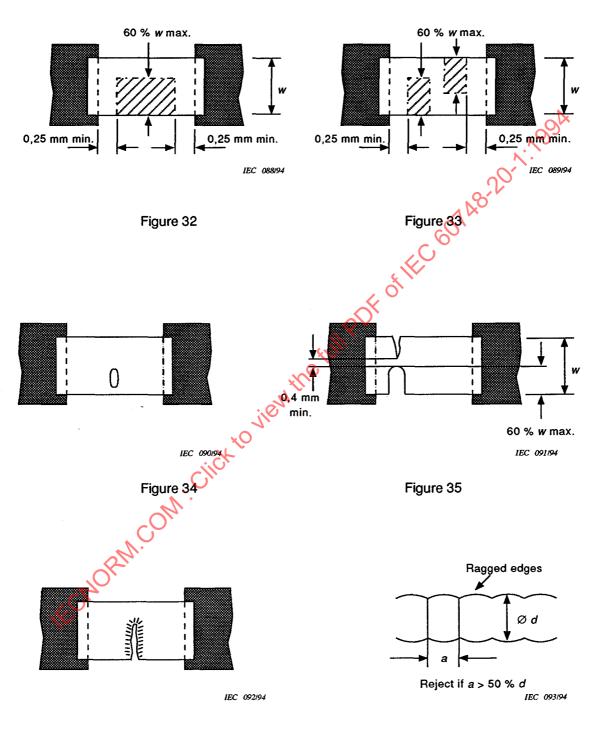

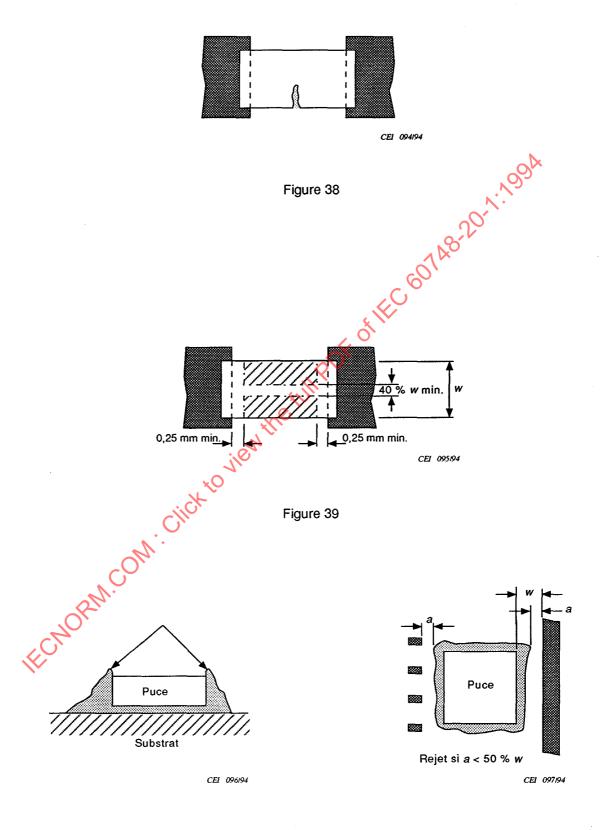

#### 2) résistances ajustées par laser

- la largeur minimale d'une résistance restant après ajustage doit être de 40 % (voir figure 26) sauf quand il apparaît que la densité maximale usuelle autorisée par les règles de conception n'est pas dépassée;

- pontage pour la découpe d'ajustage sauf si elle est prévue par conception (voir figure 34);

- éraflure, entaille ou manque combine avec l'ajustage selon les exigences ci-dessus concernant la largeur minimale de résistance (voir figure 35);

- microfissure (voir figure 36);

- bordures grossières du matériau de résistance (voir figure 37). (Toute marche doit être inférieure ou égale à 50 % du diamètre du faisceau laser);

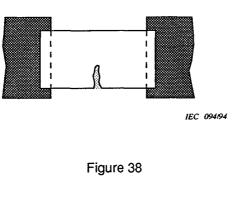

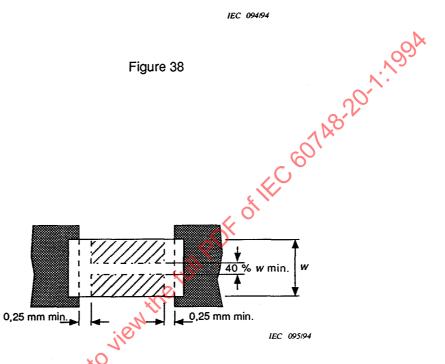

- résidu du matériau de résistance dans la découpe d'ajustage (voir figure 38);

- zone d'ajustage pour les découpes unilatérales (simple encoche, double encoche, coupe en «L», coupe en «L» graduée (figure 32) ou pour les coupes bilatérales (coupe serpentin, coupe en double «L» (figures 33 et 39) hors spécification des figures 32, 33 et 39).

### 3 Assemblage – Fixation mécanique et connexion électrique des parties du substrat

#### 3.1 Composants rapportés

Voir les spécifications relatives aux composants ou pièces détachées.

#### 3.2 Méthode d'assemblage – Faible grossissement

Aucun dispositif ne doit être accepté s'il présente les défauts suivants:

#### 3.2.1 Généralités

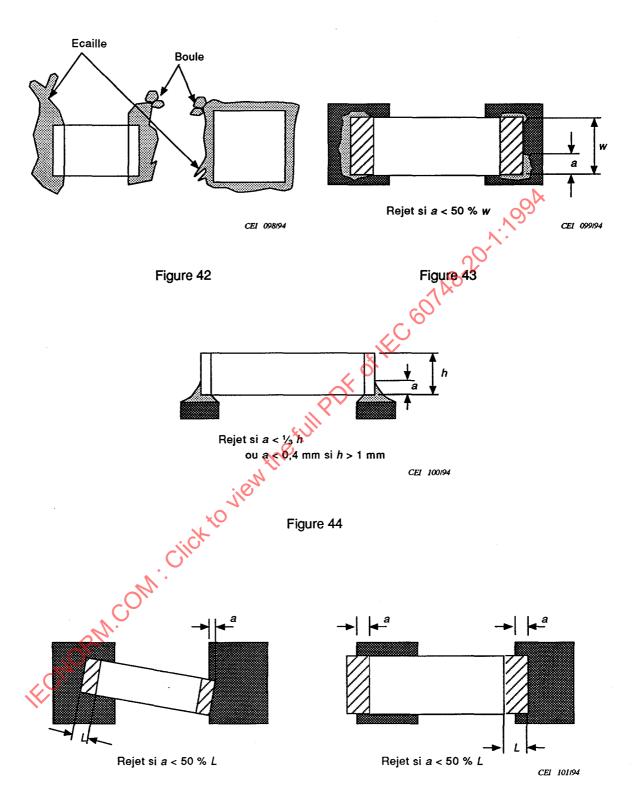

- boule ou écaille du matériau de fixation (voir figure 42);

- projection du matériau de fixation ou du matériau étranger non mouillé en surface;

#### 2.2.3.2 Trimmed resistors

No device shall be acceptable that shows failures as described in 2.2.3.1 or the following:

#### 1) abrasion trimmed resistors

- the minimum resistor width remaining after trimming shall be 40 % (see figure 26), except where it can be shown that the maximum current density permitted by the design rules are not exceeded;

- width of the termination reduced by more than 50 % (see figure 27);

- bridging of the trim-cut (see figure 28);

- a scratch, nick or void opposite a trim kerf which reduces the resistors width to

40 % (see figure 29);

- micro cracking and ragged edges in the resistor material (see figure 30);

- residue of resistor material in the trim-cut (see figure 31);

#### 2) laser trimmed resistors

- the minimum resistor width remaining after trimming shall be 40 % (see figure 26), except where it can be shown that the maximum current density permitted by the design rules are not exceeded;

- bridging of the trim-cut unless required by the design (see figure 34);

- a scratch, nick or void, in combination with a trim in accordance with requirement above on minimum undisturbed resistor width (see figure 35);

- micro-cracking (see figure 36);

- ragged edges in the resistor material (see figure 37). (Any step shall be less than or equal to 50 % of the laser spot diameter);

- residue of resistor material in the trim-cut (see figure 38);

- trimming area for one side entering cuts (plunge-cut, double plunge-cut, "L"-cut with vernier (figure 32) or for two sides entering cuts (serpentine cut, double "L"-cut (figures 33 and 39) not in the field as specified in figures 32, 33 and 39).

#### 3 Assembly – Mechanical attachment and electrical connection of parts to the substrate

#### 3.1 Added components

See relevant specifications of the component or part.

#### 3.2 Assembly method - Low magnification

No device shall be acceptable that shows the following:

#### 3.2.1 General

- balling or flaking of the attachment material (see figure 42);

- loose residue of the attachment material or unwetted foreign material on its surface;

- accumulation du matériau de fixation s'étendant au-delà ou touchant le haut de la surface du composant (voir figure 40);

- distance d'isolement entre un matériau de fixation conducteur et un conducteur adjacent réduite à moins de 50 % de la distance d'isolement entre les éléments du circuit (voir figure 41).

#### 3.2.2 Soudure et attache eutectique

- présence de résidu de flux;

- présence de fêlures, cratères et manques dans le cordon de soudure;

- 1) pour résistances et condensateurs en pastilles

- sorties et plots conducteurs sur substrat ne dépassant pas de plus de 50 % la longueur «L» de sortie du composant (voir figure 45);

- 2) pour les résistances et condensateurs en pastilles dont les bornes de sortie permettent le mouillage de soudure perpendiculaire au substrat

- cordon sur moins de 50 % de chaque face de périmètre mouillable (voir figure 43);

- hauteur du cordon de soudure inférieure à un tiers de la hauteur ou à 0,4 mm si celle-ci excède 1 mm (voir figure 44);

- 3) pour les résistances et condensateurs en pastilles dans les bornes de sorties ne permettent pas le mouillage soudure perpendiculaire au substrat

- soudure apparente à moins de 75 % du contour mouillable;

- à l'endroit où le contour mouillable qui a été conçu est tellement éloigné du bord du composant qu'il est impossible de procéder à un examen visuel du mouillage; d'autres méthodes d'examen doivent être acceptées par l'Organisme National de Surveillance (ONS). Un exemple de méthode d'essai de substitution acceptable est l'application d'une contrainte de cisaillement de la soudure qui soit plus grande que celle produite par la force d'arrachement prescrite par la spécification particulière correspondante, par exemple en utilisant une jauge de mesure de force, sur une base d'échantillonnage convenable;

- 4) pour les pastilles de semiconducteurs

- cordon de soudure ou de matériau eutectique mouillé à environ moins de 50 % du périmètre du composant ou mouillage continu sur deux faces du composant, quel que soit le plus petit;

- 5), (pour les composants aux connexions préformées pour le montage en surface

- positionnement du composant sur le plot du conducteur de telle sorte que le mouillage de 50 % du périmètre de la connexion mouillable ne puisse être atteint (voir figures 47 et 48);

- débordement inférieur à 50 % de la ou des connexions sur le ou les plots du conducteur sur le substrat (voir figure 46);

- longueur du cordon de soudure inférieure à 75 % du contour visible (2a + b) (voir figure 47);

- moins de 75 % de la longueur de la connexion et moins de 50 % de l'épaisseur de la connexion mouillée (voir figure 48);

- attachment material build-up that extends above or touches the top surface of the component (see figure 40);

- insulation distance between a conductive attachment material and an adjacent conductor reduced to less than 50 % of the insulation distance between circuit elements (see figure 41).

- 3.2.2 Soldering and eutectic attachment

- presence of any flux residues;

- presence of cracks, craters and voids in the solder fillet;

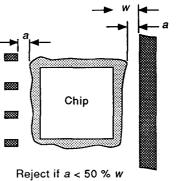

- 1) for resistor and capacitor chips

- end terminations and conductor pads on substrate not overlapping by at least 50 % of the component termination length "L" (see figure 45);

- 2) for resistor and capacitor chips having termination areas intended to allow solder wetting perpendicular to the substrate

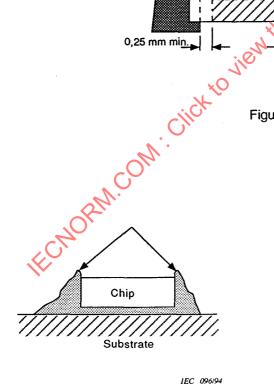

- fillet on less than 50 % of each wettable perimeter face (see figure 43);

- height of the solder fillet less than one third of height or less than 0,4 mm if height is greater than 1 mm (see figure 44);

- 3) for resistor and capacitor chips having terminations with no wettable surfaces perpendicular to the substrate

- solder visible less than 75 % of the wettable periphery;

- where the designed wettable periphery is so far from the component edge that visual inspection of wetting is impracticable, alternative inspection methods shall be agreed by the National Supervising Inspectorate (NSI). An example of an acceptable alternative is the application of a shear stress in the solder which is greater than that produced by the acceleration force prescribed by the relevant detail specification, for example, using a force measurement gauge, on a suitable sampling basis;

- 4) for semiconductor dice

- fillet of solder or eutectic material wetted around less than 50 % of the component perimeter or continuous wetting on two sides of the component, whichever is less;

- 5) for components with preformed leads for surface mounting

- positioning of the component on the conductor pads such that wetting of 50 % of the wettable lead perimeter cannot be achieved (see figures 47 and 48);

- less than 50 % overlap of component lead(s) on conductor pad(s) on the substrate (see figure 46);

- solder fillet length less than 75 % of the visible periphery (2a + b) (see figure 47);

- less than 75 % of the lead length and less than 50 % of the thickness of the lead wetted (see figure 48);

- 6) pour les composants avec des connexions montées dans des trous

- moins de 50 % de la circonférence de la section circulaire de la sortie mouillée et/ou du plot de connexion du substrat (voir figure 49).

#### 3.2.3 Adhésif organique

matériau polymère organique ou résidu sur plots conducteurs de substrats ou fil de liaison.

# 4 Assemblage – Fixation mécanique et connexion électrique du substrat au boîtier – Faible grossissement

Aucun dispositif ne doit être accepté s'il présente les défauts suivants:

#### 4.1 Généralités

- substrat non positionné conformément au schéma correspondant (voir figure 50);

- substrat attaché sous le ou les supports du boîtier qui est/sont en contact visuel avec le substrat ou distance entre un conducteur non passivé sur le substrat et les supports du boîtier inférieure à 50 % de la distance minimale d'isolement entre les éléments du circuit (voir figure 51).

#### 4.2 Soudure et adhésif organique

- matériel de fixation non visible à au moins 50 % du périmètre du substrat à moins qu'il ne soit continu sur deux côtés non adjacents du substrat (voir figure 52);

- matériel de fixation conducteur sur la partie supérieure du substrat qui réduit la distance entre le bord du substrat et une partie fonctionnelle du circuit de moins de 50 % de la distance minimale d'isolement entre les éléments du circuit (voir figure 53);

- boule ou écaille du matériel de fixation (voir figure 54);

- projection du matériau de fixation;

- matériau de fixation non conducteur sur la partie supérieure du support du boîtier (à l'étude);

- accumulation du matériau conducteur de fixation qui s'approche à plus de 0,25 mm des supports du boîtier;

- matériau de soudure ou d'alliage sur le plot de connexion du substrat qui laisse une zone inférieure à deux fois celle de la taille maximale permise pour le passage de ce matériau;

- présence de tout flux résiduel;

- résidu polymère organique sur plots de connexion ou soudure mis en évidence par décoloration.

- 6) for components with leads for through-hole mounting

- less than 50 % of the circumference of a circular section lead wetted to lead and/or substrate pad (see figure 49).

#### 3.2.3 Organic adhesive

- organic polymer material or residue on substrate conductor pads or bonding wire.

# 4 Assembly – Mechanical attachment and electrical connection of substrate to package – Low magnification

No device shall be acceptable that shows the following:

#### 4.1 General

- substrate not positioned in accordance with the relevant layout drawing (see figure 50);

- substrate attached under package post(s) which is/are in visual contact with the substrate or distance between an unpassivated conductor on the substrate and the package post(s) less than 50 % of the minimum insulation distance between circuit elements (see figure 51).

#### 4.2 Soldering and organic adhesive

- attachment material not visible around at least 50 % of the substrate perimeter unless it is continuous on two full non-adjacent sides of the substrate (see figure 52);

- conductive attachment material on top surface of the substrate that reduces the distance between the edge of the substrate and any operating portion of the circuit by less than 50 % of the minimum insulation distance between circuit elements (see figure 53);

- balling or flaking of the attachment material (see figure 54);

- loose residue of the attachment material;

- non-conductive attachment material on top surface of the package post (under consideration);

- conductive attachment material build-up that comes closer than 0,25 mm to package posts;

- solder or alloy material on substrate bonding pad that leaves an area less than twice the maximum allowable bonding size free of such material;

- presence of any residual flux;

- organic polymer residue on bonding or soldering pads evident by discolouration.

#### 5 Interconnexions de fils

#### 5.1 Généralités

Cet article recouvre les exigences en matière d'examen des connexions de fils sur des composants rapportés, des substrats et bornes de boîtier. L'examen de connexion des fils est normalement réalisé avec un grossissement minimum de 60 x.

#### 5.2 Soudure par boule d'or et en lingot

Aucun dispositif ne doit être accepté s'il présente les défauts suivants:

- moins de 50 % de la soudure de la pastille sur la surface du plot de connexion;

- des soudures sur la borne du boîtier ou le substrat ne se trouvant pas complètement à l'intérieur de la surface du plot de connexion;

- des soudures par boules des pastilles de semiconducteurs placées de telle sorte que la séparation, entre les soudures ou entre la soudure et la métallisation fonctionnelle non vitrifiée qui ne lui est pas connectée, soit inférieure à 20 μm.

Pour une métallisation fonctionnelle vitrifiée, l'espace minimal ne doit pas être inférieur à 2,5 μm.

### 5.3 Soudure par boule d'or

Aucun dispositif ne doit être accepté s'il présente les défauts suivants:

- soudure par boule d'or dont les diamètres sont inférieurs à 2 fois le diamètre des fils ou 5 fois supérieurs;

- soudure par boule d'or dont les sorties de fils ne sont pas complètement à l'intérieur du contour des boules d'or;

- soudure par boule d'or dont les centres de sorties ne sont pas dans les limites des plots de connexion.

#### 5.4 Soudure sans queue (en croissant)

Aucun dispositif ne doit être accepté s'il présente les défauts suivants:

- des soudures sans queue dont la largeur est inférieure à 1,2 fois le diamètre de fil ou lui est 5 fois supérieure, ou dont la longueur est inférieure à 0,5 fois le diamètre de fil ou lui est 3 fois supérieure (voir figure 55);

- des soudures sans queue dont l'empreinte de l'outil ne couvre pas toute la largeur du fil (voir figure 55);

- des soudures sans queue au point où la métallisation sort de la zone de soudure et qui ne présente pas une ligne de métal ininterrompue entre le contour du lien et au moins un côté de la bande de métallisation qui arrive (voir figure 55).

#### 5 Wire interconnections

#### 5.1 General

This clause covers the requirements for inspection of wire bonds on added components, substrates and package post. The wire bond inspection is normally performed at a minimum magnification of  $60 \times 10^{-5}$

#### 5.2 Gold ball and wedge bonds

No device shall be acceptable that shows the following:

- less than 50 % of the bond on the die within the bond pad area;

- bonds on the package post or substrate not completely within the bond pad area;

- bond balls on semiconductor dice placed such that the separation between bonds, or between the bond and the unglassivated operating metallization not connected to it, is less than 20  $\mu m$ .

For glassivated operating metallization, the minimum spacing shall be not less than  $2.5 \ \mu m$ .

#### 5.3 Gold ball bonds

No device shall be acceptable that shows the following:

- ball bonds of which the diameters are less than 2 times or exceed 5 times the wire diameters;

- ball bonds of which the wire exits are not completely within the ball peripheries;

- ball bonds of which the centre exits are not within the boundaries of the bonding pads.

# 5.4 Tail-less (crescent) bonds

No device shall be acceptable that shows the following:

- tail-less bonds the width of which is less than 1,2 times or greater than 5,0 times the wire diameter or the length of which is less than 0,5 times or greater than 3,0 times the wire diameter (see figure 55);

- tail-less bonds on which the tool impression does not cover the entire width of the wire (see figure 55);

- tail-less bonds at the point where metallization exits from the bonding pad do not exhibit an uninterrupted line of metal between the periphery of the bond and at least one side of the entering metallization strip (see figure 55).

#### 5.5 Soudure en lingot

Aucun dispositif ne doit être accepté s'il présente les défauts suivants:

- soudure ultrasonique de largeur inférieure à 1,2 fois le diamètre du fil ou 2,5 fois supérieure à celui-ci, ou de longueur inférieure à 1,5 fois le diamètre du fil ou 5 fois supérieure à celui-ci (voir figure 56);

- soudure thermosonique et à thermocompression de largeur inférieure à 1,5 fois le diamètre du fil ou 3 fois supérieure à celui-ci, ou de longueur inférieure à 1,5 fois le diamètre du fil ou 5 fois supérieure à celui-ci (voir figure 57);

- $-\,$  soudure au point où la métallisation sort de la zone de soudure et qui ne présente pas une ligne de métal ininterrompue entre le contour du lien et au moins un côté de la bande de métallisation qui arrive (voir figure 58) sauf si cette bande est plus large que 50  $\mu m$  et si la dimension de la zone de soudure sur le côté de la bande est supérieure à 100  $\mu m$ .

#### 5.6 Soudures superposées

Aucun dispositif ne doit être accepté s'il présente les défauts suivants:

- une soudure pour fixer deux fils communs;

- plus d'une soudure au sommet de la soudure initiale;

- soudures superposées avec une zone de contact entre la seconde soudure et la soudure initiale inférieure à 75 %.

# 5.7 Soudure des conducteurs poutres

Ces critères et exigences en matière d'examen s'appliquent à l'intégralité de la surface liée soit par contact d'un outil direct soit par couche intermédiaire adéquate.

Aucun dispositif ne doit être accepté s'il présente les défauts suivants:

- des soudures sur lesquelles la marque de l'outil ne traverse pas complètement la totalité de la largeur de la poutre;

- des soudures sur lesquelles la longueur de la marque de l'outil est inférieure à 25  $\mu$ m (voir figure 59);

- Ja marque de l'outil est inférieure à 25 μm du bord de la pastille (voir figure 60);

la surface de soudure effective est inférieure à 50 % de la surface qui serait soudée en cas de poutre exactement alignée (voir figure 60);

- les fêlures ou les déchirures dans les surfaces effectives de poutre soudées qui excèdent 25 % de la largeur originale de la poutre;

- les soudures placées de telle sorte que la séparation entre les soudures ou entre des soudures et une métallisation adjacente non vitrifiée qui ne leur est pas connectée, soit inférieure à 25 μm;

- décollement ou écaillage des soudures.

#### 5.5 Wedae bonds

No device shall be acceptable that shows the following:

- ultrasonic wedge bonds of which the widths are less than 1,2 times or greater than 2,5 times the wire diameters, or of which the lengths are less than 1,5 times or greater than 5 times the wire diameters (see figure 56);

- thermosonic and thermocompression wedge bonds of which the widths are less than 1,5 times or greater than 3 times the wire diameters, or of which the lengths are less than 1,5 times or greater than 5 times the wire diameters (see figure 57);

- wedge bonds at the point where metallization exits from the bonding pad that do not show a line of undisturbed metal between the periphery of the bond and at least one side of the entering metallization strip (see figure 58) except when this strip is wider than 50 μm and the bond pad dimension on the side of the strip is greater than 100 μm.

#### 5.6 Compound bonds

No device shall be acceptable that shows the following:

- one bond to secure two common wires;

- more than one bond on top of original bond;

- OT IEC GOT ABIN - compound bonds with contact area between second bond and original bond less than 75 %.

#### 5.7 Beam lead bonds

These inspection criteria and requirements apply to the complete area bonded by either direct tool contact or a compliant intermediate layer.

No device shall be acceptable that shows the following:

- bonds on which the tool impression does not completely cross the entire beam width:

- bonds on which the tool impression length is less than 25 µm (see figure 59);

- bonding tool impression less than 25 µm from the die edge (see figure 60);

- effectively bonded area less than 50 % of area which could be bonded in case of an exactly aligned beam (see figure 60);

- cracks or tears in effective bonded beam area exceeding 25 % of original beam width:

- bonds placed such that separation between bonds, or between bonds and adjacent unglassivated metallization not connected to them, is less than 25 µm;

- bonds lifting or peeling.

#### 5.8 Critères pour les fils

Aucun dispositif ne doit être accepté s'il présente les défauts suivants:

- 1) tout fil touchant un autre fil (à l'exclusion des fils communs), l'emballage, la métallisation non vitrifiée, la puce ou toute partie du boîtier;

- 2) une boucle ou un pliage excessif dans un des fils, de telle sorte qu'il se rapproche de plus de deux diamètres de fil d'un autre fil, de l'emballage, de la métallisation non vitrifiée, de la puce ou d'une partie du boîtier à laquelle il ne devrait pas être connecté;

- 3) des entailles, coupures, plis, éraflements, coudes dans un des fils réduisant son diamètre de plus de 25 %;

- 4) un fil supplémentaire ajouté ayant une longueur supérieure à deux diamètres de fil au plot de soudure ou une longueur supérieure à quatre diamètres de fil au support de boîtier;

- 5) une déchirure à la jonction entre le fil et la soudure;

- 6) tout fil courant en droite ligne du plot de soudure de la pastille au support du boîtier sans faire d'arc. Toute boule d'or d'où le fil ne sort pas verticalement sur une distance d'au moins un diamètre de fil avant de faire un arc vers le support du boîtier/la sortie du boîtier;

- 7) un ou des fils croisant un autre ou d'autres fils (à l'exception des conducteurs communs);

- Matériau étranger cick to vient the full stude. 8) un ou des fils non conformes au schéma de soudure.

A l'étude.

ECHORNI COM!

A l'étude.

#### 5.8 Criteria for wires

No device shall be acceptable that exhibits:

- 1) any wire touching another wire (excluding common wires), package post, unglassivated operating metallization, die, or any portion of the package;

- 2) excessive loop or sag in any wire so that it comes closer than two wire diameters to another wire, package post, unglassivated operating metallization or die, or portion of the package to which it should not be connected;

- 3) nicks, cuts, crimps, scoring or neckdown in any wire that reduces the wire diameter by more than 25 %;

- 4) attached extra wire greater than two wire diameters in length at the bonding pad or four wire diameters in length at the package post;

- 5) tearing at the junction of the wire and bond;

- 6) any wire making a straight line run from die bonding pad to package post that has no arc. Any gold ball from which the wire does not exit vertically for a distance of at least one wire diameter before arcing to the package post/lead;

- 7) wire(s) crossing wire(s) (except common conductors)

- diagra, diagra 8) wire(s) not in accordance with bonding diagram

#### 6 Package conditions

Under consideration.

# Foreign material

Under consideration.

Figure 5

Figure 6

Figure 5

Figure 6

Figure 10

Figure 11

Figure 10

Figure 11

Figure 15

Figure 16

Figure 15

Figure 16

Figure 21

Figure 22

Figure 21

Figure 22

Figure 26

Figure 26

Reject if a < 40 % w

IEC 082/94

Figure 30

Figure 31

Figure 30

Figure 31

Figure 36

Figure 37

Figure 36

Figure 37

Figure 40

Figure 41

Figure 39

IEC 097194

Figure 40

Figure 41

Figure 45