# TECHNICAL REPORT

# IEC TR 62017-1

First edition 2001-04

Documentation on design automation subjects -

Part 1:

EDA Industry standards roadmap

Documentation sur les sujets d'automatisation de la conception –

Partie 1:

EDA Industry Standards roadmap

#### **Publication numbering**

As from 1 January 1997 all IEC publications are issued with a designation in the 60000 series. For example, IEC 34-1 is now referred to as IEC 60034-1.

#### Consolidated editions

The IEC is now publishing consolidated versions of its publications. For example, edition numbers 1.0, 1.1 and 1.2 refer, respectively, to the base publication, the base publication incorporating amendment 1 and the base publication incorporating amendments 1 and 2.

#### Further information on IEC publications

The technical content of IEC publications is kept under constant review by the IEC thus ensuring that the content reflects current technology. Information relating to this publication, including its validity, is available in the IEC catalogue of publications (see below) in addition to new editions, amendments and corrigenda. Information on the subjects under consideration and work in progress undertaken by the technical committee which has prepared this publication, as well as the list of publications issued, is also available from the following:

- IEC Web Site (www.iec.ch)

- Catalogue of IEC publications

The on-line catalogue on the IEC web site (www.iec.ch/catlg-e.htm) enables you to search by a variety of criteria including text searches, technical committees and date of publication. On-line information is also available on recently issued publications, withdrawn and replaced publications, as well as corrigenda.

IEC Just Published

This summary of recently issued publications (<a href="www.iec.ch/JP.htm">www.iec.ch/JP.htm</a>) is also available by email. Please contact the Customer Service Centre (see below) for turther information.

Customer Service Centre

tryou have any questions regarding this publication or need further assistance, please contact the Customer Service Centre:

Email <u>custserv@jec.ch</u> Tel: +41 22 919 02 11 Fax: +41 22 919 03 00

# TECHNICAL REPORT

# IEC TR 62017-1

First edition 2001-04

Documentation on design automation subjects -

Part 1:

EDA Industry standards roadmap

Documentation sur les sujets d'automatisation de la conception –

Partie 1:

EDA Industry standards roadmap

© IEC 2001 — Copyright - all rights reserved

No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher.

International Electrotechnical Commission 3, rue de Varembé Geneva, Switzerland Telefax: +41 22 919 0300 e-mail: inmail@iec.ch IEC web site http://www.iec.ch

PRICE CODE

# **Table of contents**

| FOREWORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| How This Book is Organized                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10               |

| How to Find the Information You Want                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10               |

| 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11               |

| 1.1 Charter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11               |

| 1.1.1 Identify the EDA Industry Requirements on EDA Systems 1.1.2 Review Status and Current Plans of Related Standards 1.1.3 Determine How to Coexist and Migrate to Improved Standards 1.1.4 Identify Standards Areas Requiring Improvement 1.1.5 Develop a Roadmap to Future Standards 1.1.6 Deliver Recommendations and Roadmap Contributions 1.1.7 EDA Standards Industry Council 1.2 Background 1.2.1 Productivity Improvement 1.2.2 Complexity Management 1.2.3 Advanced Technology Development 1.2.4 Technology Development Funding | 1111121212141414 |

| 1.3 Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15               |

| 1.3.1 Electronic Design and Test Standards Focus 1.3.2 Technology Packages 1.3.3 Design Phases 1.3.4 Key Electronic Design and Test Interfaces                                                                                                                                                                                                                                                                                                                                                                                             | 15<br>16         |

| 2 Executive Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17               |

| 2.1 Roadmaps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17               |

| 2.1.1 Introduction to Roadmap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17<br>18<br>18   |

| 2.2 Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23               |

| 2.2.1 Key Roadmap Recommendations                                                                                                                                                   | 23  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2.2 Coexistence and Migration                                                                                                                                                     |     |

| 2.2.3 Areas of Convergence                                                                                                                                                          | 27  |

| 2.2.4 Areas of Acceleration of Work                                                                                                                                                 | 29  |

| 2.2.5 Areas Where New Standards Work is Required                                                                                                                                    |     |

| 2.2.6 Areas Where Additional Roadmap Work is Required                                                                                                                               | 30  |

| 2.3 The Standards Development Process                                                                                                                                               | 30  |

| 2.3.1 Current Standards Development Environment                                                                                                                                     | 30  |

| 2.3.1 Current Standards Development Environment                                                                                                                                     | 31  |

| 3 Electronic Design and Test Environment                                                                                                                                            | 35  |

| 3.1 Emerging Paradigm Shifts                                                                                                                                                        | 35  |

| 3.1.1 Innovation in Systems Level Design (Architecture and High level Design Phases)                                                                                                | 35  |

| 3.1.2 Innovation in Design Process Management                                                                                                                                       | 35  |

| 3.1.3 Increased Codesign Across Design Disciplines                                                                                                                                  | 35  |

| 3.1.2 Innovation in Design Process Management 3.1.3 Increased Codesign Across Design Disciplines 3.1.4 New Architectural and Integration Concepts 3.1.5 Changing Business Practices | 35  |

| 3.1.5 Changing Business Practices                                                                                                                                                   | 36  |

| 3.1.5 Changing Business Practices                                                                                                                                                   | 36  |

| 3.2.1 Exploit Multiple EDA Operating Environments 3.2.2 Use Diverse Databases and Formats 3.2.3 Use Tools from Multiple Tool Vendors                                                | 36  |

| 3.2.1 Exploit Multiple EDA Operating Environments                                                                                                                                   | 36  |

| 3.2.2 Use Diverse Databases and Formats                                                                                                                                             | 36  |

| 3.2.3 Use Tools from Multiple Tool Vendors                                                                                                                                          | 37  |

| 3.2.4 Enforce Design Methodologies and Process Management                                                                                                                           | 37  |

| 3.2.5 Reduce (or Maintain) Cycle Time 3.2.6 Reduce Design Costs                                                                                                                     | 37  |

| 3.2.6 Reduce Design Costs                                                                                                                                                           | 37  |

| 3.2.7 Maximize Return-on-Investment (Price/Performance)                                                                                                                             | 37  |

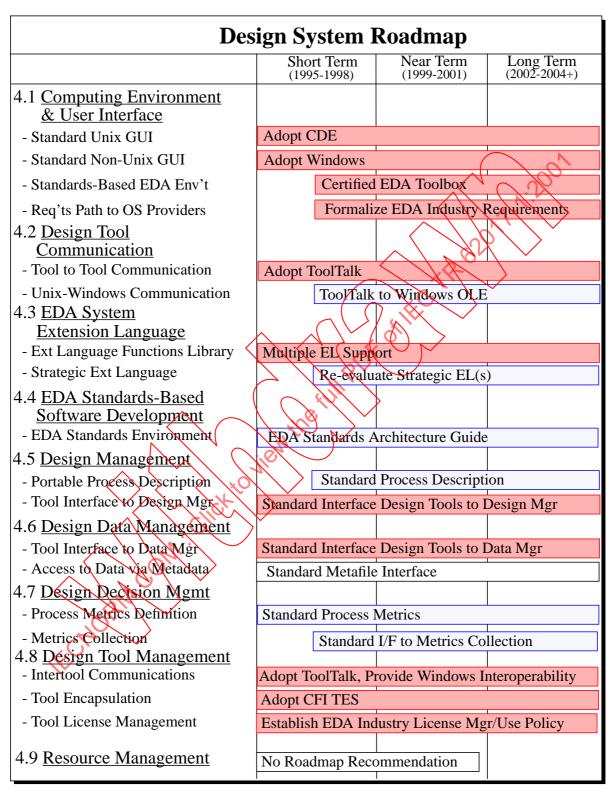

| 4 The Design System (Infrastructure and Tools)                                                                                                                                      | 39  |

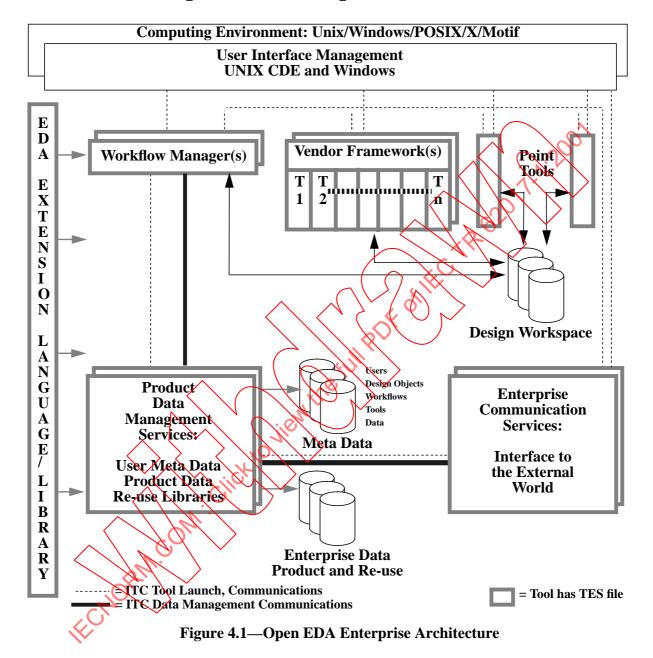

| 4.1 Computing Environment and User Interface                                                                                                                                        | 39  |

| 4.1.1 Current Environment                                                                                                                                                           | 39  |

| 4.1.2 Requirements                                                                                                                                                                  | 40  |

| 4.1.3 Recommendations                                                                                                                                                               | 41  |

| 4.1.4 Roadmap - Computing Environment and User Interface                                                                                                                            | 414 |

| 4.2 Design Tool Communication                                                                                                                                                       | 42  |

| 4.2.1 Current Environment                                                                                                                                                           | 42  |

| 4.2.2 Requirements                                                                                                                                                                  | 43  |

| 4.2.3 Recommendations                                                                                                                                                               |     |

| 4.2.4 Roadmap - Tool Communication                                                                                                                                                  | 43  |

| 4.3 EDA System Extension Language                                                                                                                                                   | 44  |

| 4.3.1 Current Environment                                                                                                                                                           | 44  |

| 4.3.2 Requirements                                                                                                                   | 44 |

|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.3.3 Recommendations                                                                                                                | 45 |

| 4.3.4 Roadmap - EDA System Extension Language                                                                                        | 46 |

| 4.4 EDA Standards-Based Software Development Environment                                                                             | 46 |

| 4.4.1 Current Environment                                                                                                            |    |

|                                                                                                                                      |    |

| 4.4.2 Requirements 4.4.3 Recommendations                                                                                             | 47 |

| 4.4.4 Roadmap - EDA System Basic Software Development Environment                                                                    | 47 |

| 4.5 Intellectual Property Protection for Design Data Objects                                                                         | 50 |

| 4.5.1 Current Environment                                                                                                            | 50 |

| 4.5.2 Requirements                                                                                                                   | 50 |

| 4.5.3 Recommendations                                                                                                                | 51 |

| 4.5.1 Current Environment 4.5.2 Requirements 4.5.3 Recommendations 4.5.4 Roadmap - Standards for Design Data Object Asset Protection | 51 |

|                                                                                                                                      |    |

| 4.6 Design Management  4.6.1 Current Environment  4.6.2 Requirements  4.6.3 Recommendations                                          | 51 |

| 4.6.1 Current Environment                                                                                                            | 51 |

| 4.6.2 Requirements                                                                                                                   | 52 |

| 4.6.3 Recommendations 4.6.4 Roadmap - Design Management                                                                              |    |

| 4.0.4 Roadinap - Design Management                                                                                                   | 34 |

| 4.7 Design Data Management                                                                                                           | 54 |

| 4.7.1 Current Environment 4.7.2 Requirements 4.7.3 Recommendations                                                                   | 55 |

| 4.7.2 Requirements                                                                                                                   | 56 |

| 4.7.3 Recommendations                                                                                                                | 57 |

| 4.7.4 Roadmap - Design Data Management                                                                                               | 57 |

| 4.8 Design Process Metrics Management                                                                                                | 57 |

| 4.8.1 Current Environment                                                                                                            | 58 |

| 4.8.2 Requirements                                                                                                                   | 58 |

| 4.83 Recommendations                                                                                                                 | 58 |

| 4.8.4 Roadmap - Design Process Metrics Management                                                                                    | 58 |

| 4.9 Design Tool Management                                                                                                           | 59 |

| 4.9.1 Current Environment                                                                                                            |    |

| 4.9.2 Requirements                                                                                                                   |    |

| 4.9.3 Recommendations                                                                                                                |    |

| 4.9.4 Roadmap - Design Tool Management                                                                                               |    |

| 4.10 Resource Management                                                                                                             | 63 |

| 4.10.1 Current Environment                                                                                                           | 63 |

| 4.10.2 Requirements                                                                                                                  | 63 |

| 4.10.3 Recommendations                                                                                                               |    |

| 4.10.4 Roadmap - Design Resource Management               | 64 |

|-----------------------------------------------------------|----|

| The Design Information (Design Data Representation)       | 65 |

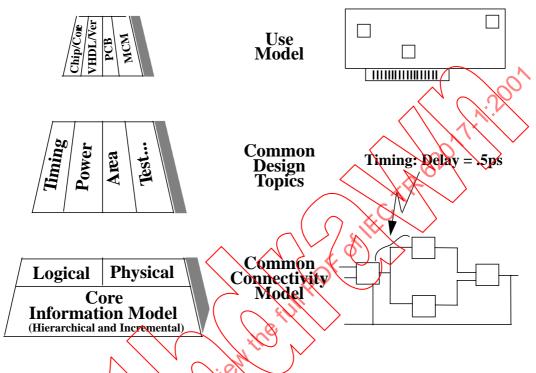

| 5.1 Common Topics Across All Design Information           | 65 |

| 5.1.1 Incremental Processing                              |    |

| 5.1.2 Hierarchical Processing                             |    |

| 5.1.3 Design Object Naming                                | 68 |

| 5.2 Common Topics Across All Design Steps                 | 69 |

| 5.2.1 Timing Information                                  | 69 |

| 5.2.2 Simulation and Test Control                         | 73 |

| 5.3 System Level Design                                   | 75 |

| 5.3.1 Current Environment                                 | 75 |

| 5.3.1 Current Environment                                 | 75 |

| 5.3.3 Recommendations                                     | 77 |

| 5.3.3 Recommendations 5.3.4 Roadmap - System Level Design |    |

| 5.4 Detailed Design                                       | 79 |

| 5.4.1 Current Environment                                 |    |

| 5.4.2 Dequirements                                        | 80 |

| 5.4.3 Recommendations                                     | 86 |

| 5.4.3 Recommendations 5.4.4 Roadmap - Detailed Design     | 86 |

| 5.5 Design and Technology Re-use                          | 88 |

| 5.5.1 Environment                                         | 88 |

| 5.5.2 Requirements                                        | 89 |

| 5.5.3 Recommendations                                     | 92 |

| 5.5.4 Roadmap - Design and Technology Re-Use              | 92 |

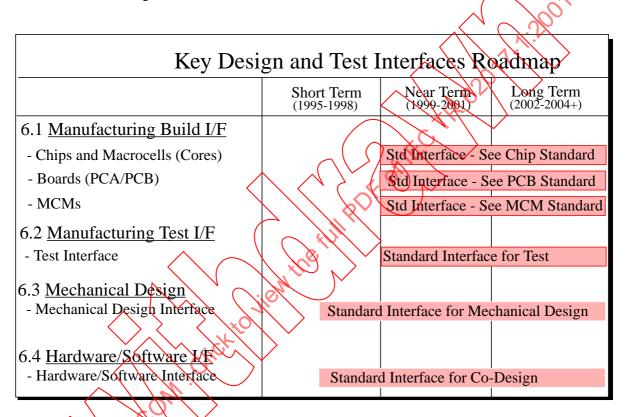

| 6 Key Electronic Design and Test Interface                | 96 |

| 6.1 Manufacturing Build Interface                         | 96 |

| 6.1.1 Current Environment                                 | 96 |

| 6.1.2 Requirements                                        | 96 |

| 6.1.3 Recommendations.                                    |    |

| 6.1.4 Roadmap - Manufacturing Build Interface             | 97 |

| 6.2 Manufacturing Test Interface                          | 98 |

| 6.2.1 Current Environment                                 | 98 |

| 6.2.2 Requirements                                        |    |

| 6.2.3 Recommendations                                     |    |

| 6.2.4 Roadmap - Manufacturing Test Interface              | 99 |

| 6.3 Mechanical Design Interface                           | 99 |

| 6.3.1 Current Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 99  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.3.2 Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 99  |

| 6.3.3 Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 6.3.4 Roadmap - Mechanical Design Interface .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 0.3.4 Roadmap - Mechanical Design Interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100 |

| 6.4 Software Design Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 100 |

| 6.4.1 Current Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 6.4.2 Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 6.4.3 Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 6.4.4 Decemendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 102 |

| 6.4.4 Roadmap - Software Design Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 102 |

| Appendix A - The Roadmap Working Groups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 103 |

| It Charles and the state of the |     |

# **List of Tables**

| Table 2.1: Areas of Recommended Standards Convergence          | . 28 |

|----------------------------------------------------------------|------|

| Table 2.2: Areas of Recommended Standards Acceleration         | . 29 |

| Table 2.3: Areas of Recommended New Standards Work             | . 29 |

| Table 2.4: Areas of Recommended Additional Roadmap Development | . 30 |

| Table 5.1: Impact of Design Size on Design Processing Times    | . 81 |

|                                                                | 105  |

| Table A.2: Design and Data Management Working Group (DDM)      | 106  |

| Table A.2: Design and Data Management Working Group (DDM)      | 107  |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

| $\langle \rangle \rangle \langle \langle \rangle \rangle$      |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

|                                                                |      |

# **List of Figures**

| Figure 2.1— Design System Roadmap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.2— Design Information Roadmap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 2.3— Key Design and Test Interfaces Roadmap23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

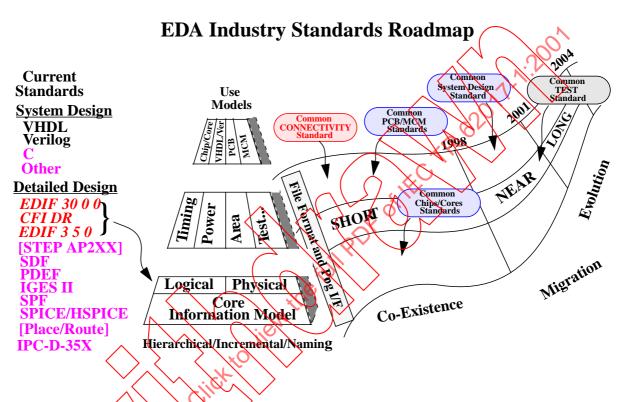

| Figure 2.4— The EDA Industry Standards Roadmap25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 2.5— Vision of Standards Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

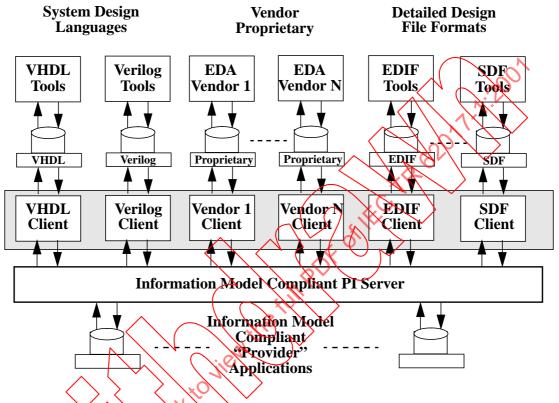

| Figure 4.1— Open EDA Enterprise Architectue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 4.2— Open EDA Data Interoperability Architectue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Condition of the second of the |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

# DOCUMENTATION ON DESIGN AUTOMATION SUBJECTS – Part 1: EDA Industry Standards Roadmap

#### **FOREWORD**

- 1) The IEC (International Electrotechnical Commission) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of the IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, the IEC publishes International Standards. Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. The IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of the IEC on technical matters express as hearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested National Committees.

- 3) The documents produced have the form of recommendations for international use and are published in the form of standards, technical specifications, technical reports or guides and they are accepted by the National Committees in that sense.

- 4) In order to promote international unification, IEC National Complittees undertake to apply IEC International Standards transparently to the maximum extent possible in their national and regional standards. Any divergence between the IEC Standard and the corresponding national or regional standard shall be clearly indicated in the latter.

- 5) The IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with one of its standards.

- 6) Attention is drawn to the possibility that some of the elements of this technical report may be the subject of patent rights. The IEC shall not be held responsible for dentifying any or all such patent rights.

The main task of IEC technical committees is to prepare International Standards. However, a technical committee may propose the publication of a technical report when it has collected data of a different kind from that which is normally published as an International Standard, for example "state of the art"

IEC 62017-1, which is a technical report, has been prepared by IEC technical committee 93: Design automation.

It is based on the EDA Industry Standards Roadmap - 1996 developed jointly by Silicon Integration Initiative Inc. (formerly CAD framework initiative, Inc.), EDAC and SEMATECH.

The text of this technical report is based on the following documents:

| Enquiry draft | Report on voting |

|---------------|------------------|

| 93/97/CDV     | 93/113/RVC       |

Full information on the voting for the approval of this technical report can be found in the report on voting indicated in the above table.

This publication has not been drafted in accordance with the ISO/IEC Directives, Part 3.

This document which is purely informative is not to be regarded as an International Standard.

The committee has decided that the contents of this publication will remain unchanged until 2004. At this date, the publication will be

- · reconfirmed;

- withdrawn;

- · replaced by a revised edition, or

- amended.

# How this Book is Organized

This book contains six chapters, summarized below:

- Chapter 1, "Introduction," describes the charter, the three working groups that contributed to the roadmap, and the scope of the work is detailed.

- Chapter 2, "Executive Summary," summarizes the key messages to the industry council regarding the requirements and the status of EDA standards with respect to those requirements, the recommendations for standards convergence, acceleration, and new standards work, and the recommended standards roadmaps for each category of requirements. The Executive Summary is designed to summarize the information in the chapters that follow that expand upon the Electronic Design and Test area, discussing the environment, the requirements, and the status, recommendations, and roadmaps in more detail.

- Chapter 3, "Electronic Design and Test Environment," reviews environmental topics that are relevant to the effective design of complex electronic systems. Key emerging paradigm shifts in the EDA industry and many of the pressures on design and CAD integrator teams are identified and discussed.

- Chapter 4, "The Design System (Infrastructure and Tools)," includes the computing environment and user interface, design tool communication, extension language, software development environment, and the design and data management areas. These topics are primarily domain-independent topics, but with an EDA focus.

- Chapter 5, "The Design Information (Design Data Representation)," addresses the key standards related to design data representations for all key design activities, including system level design (architectural and high level design activities) and detailed design (both logical and physical design in a given technology), as well as preparation for manufacturing build and test.

- Chapter 6. Key Electronic Design and Test Interfaces," discusses the interfaces to other design (or co-design) disciplines, and the key standards that relate to those interfaces. Manufacturing build and test Interfaces, software interfaces, and mechanical design interfaces are discussed.

# How to Find the Information You Want

Below are some quick access tips to help you find the information you want to read about in this book.

- To access the *key roadmap recommendations*, their priority and timeframe, read Section 2 "Executive Summary".

- To access a given topic's detailed information including the *environment*, *requirements*, *recommendations and roadmap tasks* with descriptions, find the topic in the table of contents and go to the referenced page.

- Those topics that relate to *Design and Data Management* are located in Chapter Four, since they are related to the general design system environment.

- Topics related to *Technology Libraries and Models* are located in Chapter Five, as they are specific representations of EDA design data.

#### DOCUMENTATION ON DESIGN AUTOMATION SUBJECTS -

#### Part 1: EDA Industry Standards Roadmap

## 1 Introduction

#### 1.1 Charter

The EDA Standards Roadmap Workshop was sponsored by the CAD Framework Initiative (CFI), Electronic Design Automation Companies (EDAC), and SEMATECH with participation by interested industry groups. The Workshop was specifically aimed at developing an industry-wide roadmap for development of design and test standards within Electronic Design Automation (EDA).

There were three working groups, each charged with identifying requirements, understanding the current standards environment, and developing a roadmap to improved standards across the next decade for their area of focus:

- EDA Interoperability and Integration Working Group (EII)

- Technology Libraries and Models Working Group (TLM)

- Design and Data Management Working Group (DDM)